XilinxのFPGAボード Alveo U50には,100GbEのポートが用意されています.内蔵されている100GbEコアを使うと,結構簡単にでデータのやりとりができます.

というわけで,とりあえず,Alveo U50の100GbEを使ってみた手順の紹介です.

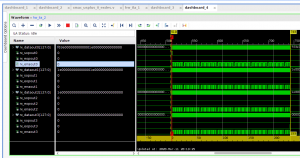

これは,およそ9000バイトのデータが233サイクル@322MHz(おそらく)で受信されてる様子.

XilinxのFPGAボード Alveo U50には,100GbEのポートが用意されています.内蔵されている100GbEコアを使うと,結構簡単にでデータのやりとりができます.

というわけで,とりあえず,Alveo U50の100GbEを使ってみた手順の紹介です.

これは,およそ9000バイトのデータが233サイクル@322MHz(おそらく)で受信されてる様子.

HBMを搭載したAlveo U50をセットアップしてみました.セットアップ対象は,x86_64の普通のパソコンです.スペックは,

OSはUbuntuで18.04で,詳細は次の通り.

$ uname -a

Linux dev-8800 4.15.0-74-generic #84-Ubuntu SMP Thu Dec 19 08:06:28 UTC 2019 x86_64 x86_64 x86_64 GNU/Linux

$ cat /etc/lsb-release

DISTRIB_ID=Ubuntu

DISTRIB_RELEASE=18.04

DISTRIB_CODENAME=bionic

DISTRIB_DESCRIPTION="Ubuntu 18.04.3 LTS"Vitisの正式サポートはUbuntu 18.04.2までなのですが,とりあえず動作は確認できました.

重要なのは,libjson-glibとunzipのインストールです.

sbtでSynthesijer.Scala開発を始めるのテンプレートを作りました.

sbt new synthesijer/sjr-scala.g8 --name=sjr-scala-test

cd sjr-scala-test

sbt runで,Synthesijer.Scalaのプロジェクトを作成,サンプルからVHDL/Verilog HDLを生成できるようになりました.

Synthesijer.Scalaは,Synthesijer内のHDLビルディングブロックをScalaを使って組み立てるライブラリです.ChiselやSpinalHDLほど細かくはいじれませんが,その分,気軽にステートマシンベースのハードウェアを設計できる…と思っています.VeriloggenのSeqとThread.Streamの間くらいかな?どうかな?

以前,シンプルなSynthesijer.Scalaの始め方(1)やシンプルなSynthesijer.Scalaの始め方(2)でも簡単に導入方法を書いたのですが,今回はもっと簡単に,sbtのマネージ依存性を使った開発手法を紹介します.

続きを読むInte PAC AFUに何か処理をオフロードする場合,当然,結果を待つ必要があります.

シンプルにMMIO読み出しを使ってポーリングで処理完了を待つのに必要な時間を afu_hello をベースに測定してみました.

hello_afuより少し複雑なサンプルとしてDMAを使ったサンプルに手をいれてみることにします.DMAを使ったサンプルはユーザロジックがQsysを使ってデザインされています.そこで,今回はQsys上に新しいコンポーネントを追加する開発フローを試してみます.

続きを読むIntel PACでは,PCIeやオンボード上のメモリなどへのアクセスがBlue bitとして提供されていて開発者はGreen bitのみの設計に注力して,アクセラレータであるAFU(Application Function Unit)を開発できるようになっています.とっても便利なのですが,その反面,想定される開発フローに乗っかれるまでは,何をどうしたものかという状態に陥ってしまいます.

まずは,hello_afuにレジスタを追加することで,独自回路をPACで動かすまでの手法を確認します.なお,本来の開発ではシミュレーションを有効に活用すべきですが,ここではシミュレータは使いません.

続きを読むKCU1500 + SDAccelの環境を再セットアップ.今度はUbuntuで構築することにしてみました.基本的な手順は,KCU1500+SCAccelの環境構築の通りなのですが,4.4.0なカーネルを利用するために一手間必要だったのでメモ.

続きを読むQflowを使ってSynthesijerで作ったLチカモジュールを合成・配置配線してみました.

ターゲットは,SynthesijerのサンプルのLチカ.カウンタだけの簡単なLチカプログラムです.Synthesijerで生成したVerilogファイルを入力に

qflow synthesize led

qflow place led

qflow routing ledとした結果をmagicでみてみると次のような感じに.とりあえず,記述としては受理されるようでよかった(中身はこれからおってみる)

arm Cortex-M1(Cortex-M0をFPGA向けに最適化したコアらしい)がXilinx FPGAで無償で利用できるという話をきいたので,試してみました.

リソースは,Easy Access to Cortex-M Processors on FPGA からアクセスできる.

XC7A35向けの合成で,リソース使用量は,

という結果.HCLKという動作クロックっぽいポートには100MHzが供給されていた.

MicroBlazeは,テンプレートで作ったササンプルデザインで,最適化オプションがPERFORMANCEで1405 Slice,最適化オプションがAreaで316 Sliceなので,Cortex-M1のリソース使用量は,その間くらいに当たるよう.

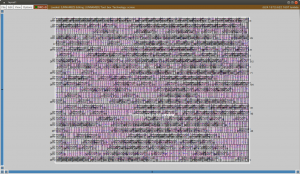

配置配線のフロアマップは下の通り.

続きを読む