XilinxのFPGAボード Alveo U50には,100GbEのポートが用意されています.内蔵されている100GbEコアを使うと,結構簡単にでデータのやりとりができます.

というわけで,とりあえず,Alveo U50の100GbEを使ってみた手順の紹介です.

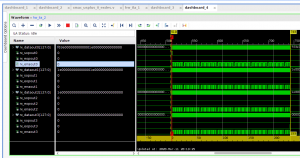

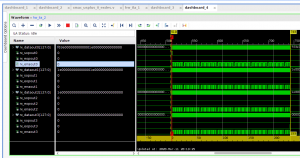

これは,およそ9000バイトのデータが233サイクル@322MHz(おそらく)で受信されてる様子.

XilinxのFPGAボード Alveo U50には,100GbEのポートが用意されています.内蔵されている100GbEコアを使うと,結構簡単にでデータのやりとりができます.

というわけで,とりあえず,Alveo U50の100GbEを使ってみた手順の紹介です.

これは,およそ9000バイトのデータが233サイクル@322MHz(おそらく)で受信されてる様子.

HBMを搭載したAlveo U50をセットアップしてみました.セットアップ対象は,x86_64の普通のパソコンです.スペックは,

OSはUbuntuで18.04で,詳細は次の通り.

$ uname -a

Linux dev-8800 4.15.0-74-generic #84-Ubuntu SMP Thu Dec 19 08:06:28 UTC 2019 x86_64 x86_64 x86_64 GNU/Linux

$ cat /etc/lsb-release

DISTRIB_ID=Ubuntu

DISTRIB_RELEASE=18.04

DISTRIB_CODENAME=bionic

DISTRIB_DESCRIPTION="Ubuntu 18.04.3 LTS"Vitisの正式サポートはUbuntu 18.04.2までなのですが,とりあえず動作は確認できました.

重要なのは,libjson-glibとunzipのインストールです.

KCU1500 + SDAccelの環境を再セットアップ.今度はUbuntuで構築することにしてみました.基本的な手順は,KCU1500+SCAccelの環境構築の通りなのですが,4.4.0なカーネルを利用するために一手間必要だったのでメモ.

続きを読むarm Cortex-M1(Cortex-M0をFPGA向けに最適化したコアらしい)がXilinx FPGAで無償で利用できるという話をきいたので,試してみました.

リソースは,Easy Access to Cortex-M Processors on FPGA からアクセスできる.

XC7A35向けの合成で,リソース使用量は,

という結果.HCLKという動作クロックっぽいポートには100MHzが供給されていた.

MicroBlazeは,テンプレートで作ったササンプルデザインで,最適化オプションがPERFORMANCEで1405 Slice,最適化オプションがAreaで316 Sliceなので,Cortex-M1のリソース使用量は,その間くらいに当たるよう.

配置配線のフロアマップは下の通り.

続きを読むうっかりyum updateしてしまったCentOSにSDAccel環境を構築しました.スペックはこんな感じ.

ドライバのインストールにこんな driver.patch が必要でした,というメモ.

続きを読む