Qflowを使ってSynthesijerで作ったLチカモジュールを合成・配置配線してみました.

ターゲットは,SynthesijerのサンプルのLチカ.カウンタだけの簡単なLチカプログラムです.Synthesijerで生成したVerilogファイルを入力に

qflow synthesize led

qflow place led

qflow routing ledとした結果をmagicでみてみると次のような感じに.とりあえず,記述としては受理されるようでよかった(中身はこれからおってみる)

Qflowを使ってSynthesijerで作ったLチカモジュールを合成・配置配線してみました.

ターゲットは,SynthesijerのサンプルのLチカ.カウンタだけの簡単なLチカプログラムです.Synthesijerで生成したVerilogファイルを入力に

qflow synthesize led

qflow place led

qflow routing ledとした結果をmagicでみてみると次のような感じに.とりあえず,記述としては受理されるようでよかった(中身はこれからおってみる)

FPGAマガジン No.11に掲載していただいた”Synthesijerを使ったFPGA上でのグラフィックス・プログラミング”という記事に使ったサンプル一式をアーカイブにまとめました.執筆当時くらいから,HDLライブラリのポート宣言方法などが変更になったため多少掲載コードと異なっています.

サンプルでは,HDMI出力部分をXilinx XAPP495で紹介されているコードを利用していますので,手元で合成する場合には,あらかじめXAPP495関連リソースをダウンロードしておく必要があります.

ちなみに,グラフィクスの事例としては,

が,とても楽しく仕上げられています.

開発プロジェクトをGitHubに移行しました.

JJUG CCC 2015 SpringというJavaユーザの集まりで、Synthesijerについて発表させていただきました。

Javaユーザに聞いていただくということで、普段よりも導入として専用HWの位置付けの部分を厚めに、また、実際にどう作っているかOpenJDK的への手のいれかたを書いてみました。

先日開催された人工知能とハードウェア・ソフトウェア協調設計ワークショップで発表された杉本さんのZynq + Vivado HLSというチュートリアルがとても素晴らしい内容だったので,それにならってZynq + Synthesijerというガイドを書いてみました.RTLは,ほとんど書かなくて大丈夫です.

たばたさんと共同で主催させてもらった,高位合成友の会でSynthesijerについて発表させていただきました.

たばたさんのneon light compiler,高前田先生@NAISTのPyCoRAMの話も大変面白く開発意欲がかき立てられた一日になりました.

さて,スライドでも紹介した演算のチェイニングを早くリリースできるよう実装すすめないと.

変更しました.

これでJDK 8な環境で実行した時の大量の警告の発生が止まります.JDK7環境では使えなくなりますが.

バイナリパッケージ(JAR)は未リリースですが今月末には.

あけましておめでとうございます.

本年もSynthesijerおよびわさらぼをよろしくお願いいたします.

さて,タイトルの通りですが,

Synthesijerのユーザーズマニュアル相当のドキュメントを書き始めました.

まだまだ書かなければならなそうな項目を挙げつらったというレベルですが,

随時アップデートしていくつもりです.

こちらからどうぞ.

Synthesijerのサンプルに含まれているsample/bench以下には、素数を並べるサンプル(Prime.java)、ソートのサンプル(BubbleSort, MergeSort)が入っています。

このサンプルをWindows(Cygwin環境)で試してみました。

注意 SYNTHESIJERのパスはcygwinでなく、Windowsでたどれる必要があります。相対パスで指定するのが問題に遭遇しにくいです。

https://www.youtube.com/watch?v=8YOWdvW_IAc を参考に、Downloading GHDLをダウンロードしてインストール。

Cygwinから呼び出せるように下記のようにして実行パスに追加。

export PATH=/cygdrive/c/Program\ Files\ \(x86\)/Ghdl/bin:$PATHGtkWaveからgtkwave-3.3.64-bin-win32.zipをダウンロード。こちらは展開するだけ。私の場合は展開したファイル一式を~/Applications/に移動して、

export PATH=~/Applications/gtkwave-3.3.64-bin-win32/gtkwave/bin:$PATHとパスを通しました。

これらのサンプルではコード内部で配列を使っています。Makefileでは、相対パス

../../lib/vhdl/dualportram.vhdなパスに配列に相当するメモリのHDLコードを必要とします。これは、Synthesijerのダウンロードページのsynthesijer_lib_20141124.zipに含まれています。ダウンロードして展開、synthesijer_lib_20141124ディレクトリをlibという名前で、synthesijer_samples_20141124と同じ階層に移動してください。

準備が終わったら、makeしてシミュレーション、結果を確認すればOKです。

まずは一式をコンパイル

cd synthesijer_samples_20141124/bench

make

make ghdl32-eオプションで実行バイナリができるはずだけど、作成されなかったので-rオプションでシミュレーションする。たとえば、次のように。結構時間がかかります。

ghdl -r primesim_top --wave=primesim_top.ghw次のようなメッセージでシミュレーションが終われば、正常終了です。

primesim_top.vhd:109:8:@48823280ns:(assertion failure): Simulation End!

C:\Program Files (x86)\Ghdl\bin\ghdl.exe:error: assertion failed

C:\Program Files (x86)\Ghdl\bin\ghdl.exe:error: simulation failedgtkwaveで結果を確認してみましょう。

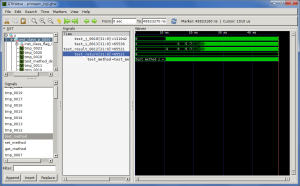

gtkwave primesim_top.ghw

実際に計算しているtestの内部変数をみてみると65521が求められていることがわかります。

ちなみに、この例では問題なくmakeできますが、java -cp に続くクラスパスの区切り文字がUnix系では:、Windowsでは;という違いがあり、Synthesijerでコンパイルするときに複数のクラスパスの指定が必要な場合には注意する必要があります。次のリリースバージョンではMakefile.cygwinを用意する予定です。

リンク先のバイナリが不安という方はご自身でコンパイルするなどの対策をしてください。責任は取れませんので…

ベーシックブロック内部並列化を組み込んだバージョンsynthesijer-20141211.jarをアップロードしました.

https://sourceforge.net/projects/synthesijer/files/synthesijer-2.0/

からダウンロードできます.