IntelがCPUでもGPUでもFPGAでも同じようにプログラミングできるOneAPIをはじめる、DevCloudで試すことができる、という話を聞いたのでためしてみました。

説明書は https://github.com/intel/FPGA-Devcloud にあるのですが、若干手順が分かりづらかったのでメモです。

続きを読むIntelがCPUでもGPUでもFPGAでも同じようにプログラミングできるOneAPIをはじめる、DevCloudで試すことができる、という話を聞いたのでためしてみました。

説明書は https://github.com/intel/FPGA-Devcloud にあるのですが、若干手順が分かりづらかったのでメモです。

続きを読むIntel PACの動作を波形レベルでデバッグしたい場合、mmlinkを使ってデバッグすることができます。新しくstpファイルを作成する場合、Intel PACにSignal Tapを仕込むの手順でデバッグ可能なFPGA用ビットファイルを作ることができます。

ですが、stpファイルと設定済のafu_synth_setup向けファイルが存在している場合に、

$ afu_synth_setup --source hw/rtl/filelist.txt build_synth

$ cd build_synth/

$ ${OPAE_PLATFORM_ROOT}/bin/run.shとゼロからビルドすると、うまくデバッグ可能なFPGA用ビットファイルを生成することができませんでした。毎回stpファイルをSignal Tap Logic Analyzerで作成しデザインに組み込むのは面倒なので、回避策が欲しいところ。というわけで、以下が回避方法です。

続きを読むIntel PACはmmlinkを使って、あたかも実機とJTAGと接続しているようにSignal Tapで信号の変化を観察してデバッグできます。

Accelerator Functional Unit Developer’s Guide for Intel(R) FPGA Programmable Acceleration Cardの6. AFU In-System Debugを見ながら作業すればよい、のですが、環境によるパラメタの設定が若干わかりづらかったので、hello_afuにSignal Tapを仕込む場合の実例を紹介します。

信号見えるまでは、何が悪いのか分からず不安ですから…

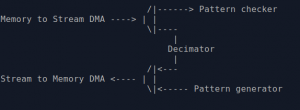

Intel PACの開発環境 inteldevstack に同梱されているサンプルのstreaming_dma_afuを試してみました。このサンプルは、

のように、PAC上のロジックに対してストリームで入出力するサンプルです(画像はサンプルのREADME.txtより・クリックで拡大)。

Inte PAC AFUに何か処理をオフロードする場合,当然,結果を待つ必要があります.

シンプルにMMIO読み出しを使ってポーリングで処理完了を待つのに必要な時間を afu_hello をベースに測定してみました.

hello_afuより少し複雑なサンプルとしてDMAを使ったサンプルに手をいれてみることにします.DMAを使ったサンプルはユーザロジックがQsysを使ってデザインされています.そこで,今回はQsys上に新しいコンポーネントを追加する開発フローを試してみます.

続きを読むIntel PACでは,PCIeやオンボード上のメモリなどへのアクセスがBlue bitとして提供されていて開発者はGreen bitのみの設計に注力して,アクセラレータであるAFU(Application Function Unit)を開発できるようになっています.とっても便利なのですが,その反面,想定される開発フローに乗っかれるまでは,何をどうしたものかという状態に陥ってしまいます.

まずは,hello_afuにレジスタを追加することで,独自回路をPACで動かすまでの手法を確認します.なお,本来の開発ではシミュレーションを有効に活用すべきですが,ここではシミュレータは使いません.

続きを読む