Intel PACはmmlinkを使って、あたかも実機とJTAGと接続しているようにSignal Tapで信号の変化を観察してデバッグできます。

Accelerator Functional Unit Developer’s Guide for Intel(R) FPGA Programmable Acceleration Cardの6. AFU In-System Debugを見ながら作業すればよい、のですが、環境によるパラメタの設定が若干わかりづらかったので、hello_afuにSignal Tapを仕込む場合の実例を紹介します。

信号見えるまでは、何が悪いのか分からず不安ですから…

準備

まずは、環境変数をセットしておきます。これは一例です。インストール状況に応じて設定内容は合わせる必要があります。ここでは、system-consoleを利用する都合上、sopc_builderにパスを通しておくのがミソです。

$ export QUARTUS_HOME=/opt/intelFPGA_pro/quartus_19.2.0b57

$ export OPAE_PLATFORM_ROOT=/home/miyoshi/inteldevstack/a10_gx_pac_ias_1_2_1_pv

$ export PATH=$QUARTUS_HOME/quartus/bin:$PATH

$ export PATH=$QUARTUS_HOME/quartus/sopc_builder/bin:$PATH最初のビルド

Signal Tapを仕込むためには.stpファイルを作成する必要がありますが、手で作成するのは面倒でGUIを使うのが簡単です。GUIを使うために、一度PACのビルドプロセスを実行してQuartusのプロジェクトファイルを生成します。

$ cd $OPAE_PLATFORM_ROOT/hw/samples/hello_afu

$ afu_synth_setup --source hw/rtl/filelist.txt build_synth

$ cd build_synth/

$ ${OPAE_PLATFORM_ROOT}/bin/run.shSignal Tapを仕込む

ビルドが終わったら.stpファイルを作ります。まずは、Quartusのプロジェクトファイルを開きます。

$ quartus build/dcp.qpf開いたら、Toolsメニューから、Signal Tap Logic Analyzerをクリックすると、Signal Tapを仕込むためのGUIが開きます。

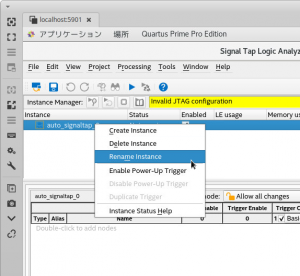

Signal Tap Logic Analyzerが起動したら、インスタンスの名前を変更します。auto_signaltap_0という名前になっているので、右クリックでコンテクストメニューを開いてRename Instanceをクリックします。

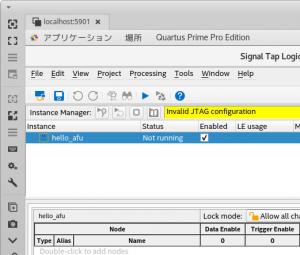

今回は、hello_afuという名前にしました。

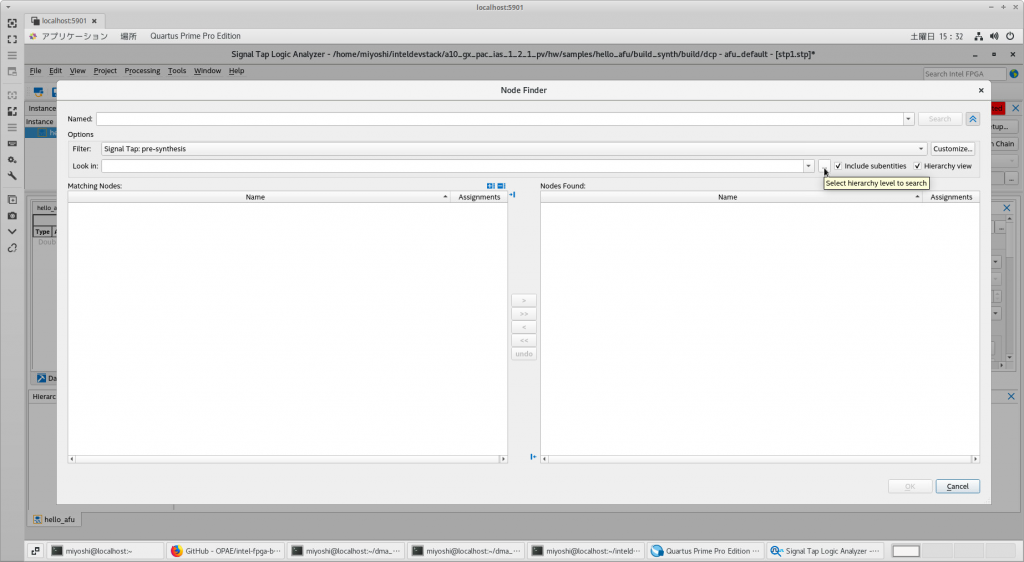

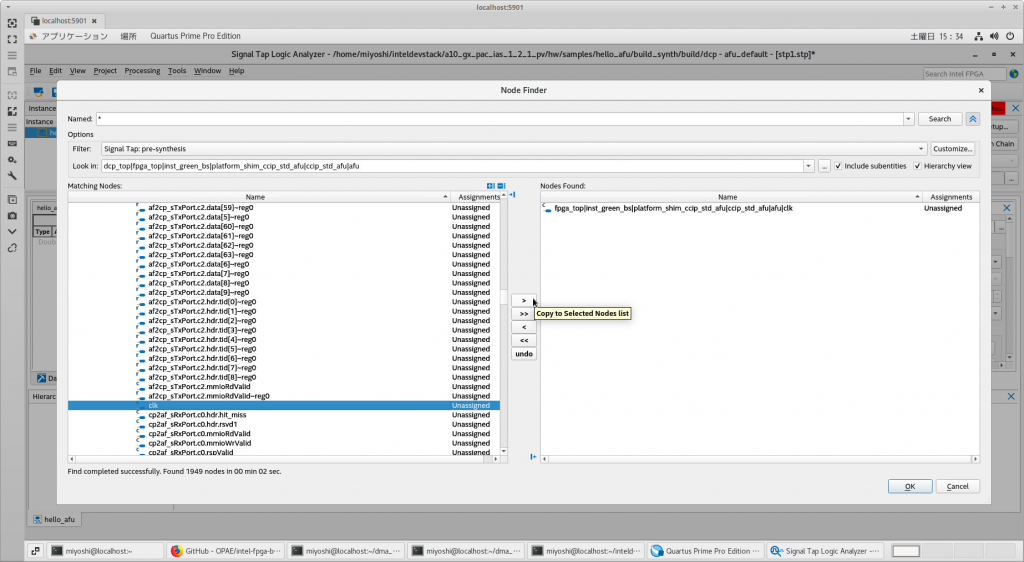

以降の手順は、ローカルでSignal Tapを利用する場合と同じです。まずは、クロックを設定します。Signal Configuration ペインの Clock: の右にあるテキストフィールドの右の … ボタンをクリックして信号選択ダイアログを開きます。

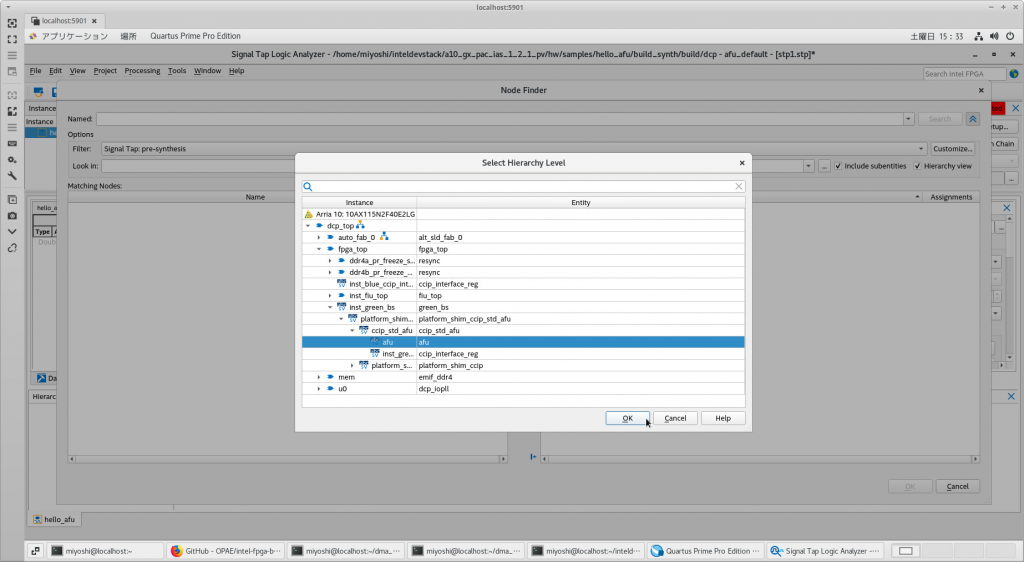

開いたら、Look in右の … ボタンをクリックして観察対象のモジュールを選択してOK、

ダイアログ上部のNamed:の右のテキストフィールドに * と入力して、Searchをクリックすると信号がずらずらと表示されるのでクロック信号(ここではclk)を探して、右矢印で選択した後、OKをクリックしてダイアログを閉じます。

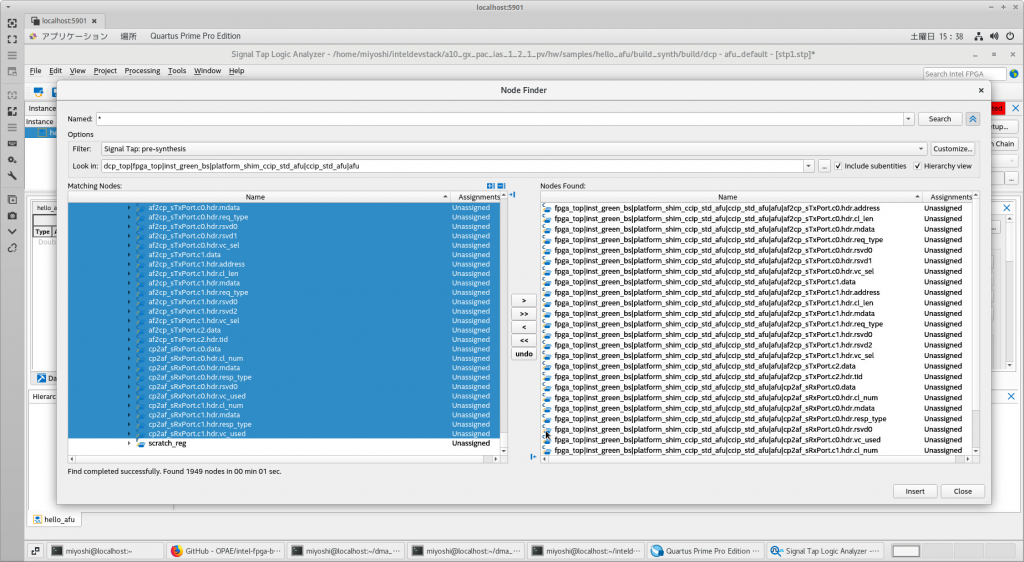

クロックを選択したら、次は観測対象の信号の選択です。真ん中左のhello_afuペインでダブルクリックすると信号選択ダイアログが開きます。同じように、Look Inで観測対象のモジュールをafuに絞って、Namedに*を入力して、Searchします。~regやIxxxという信号以外を適当に選択して、右矢印で観測対象に追加、Insertボタンをクリックして確定します。最後にCloseでダイアログを閉じます(Insertボタンをクリックしないと観測対象として追加されないので注意)

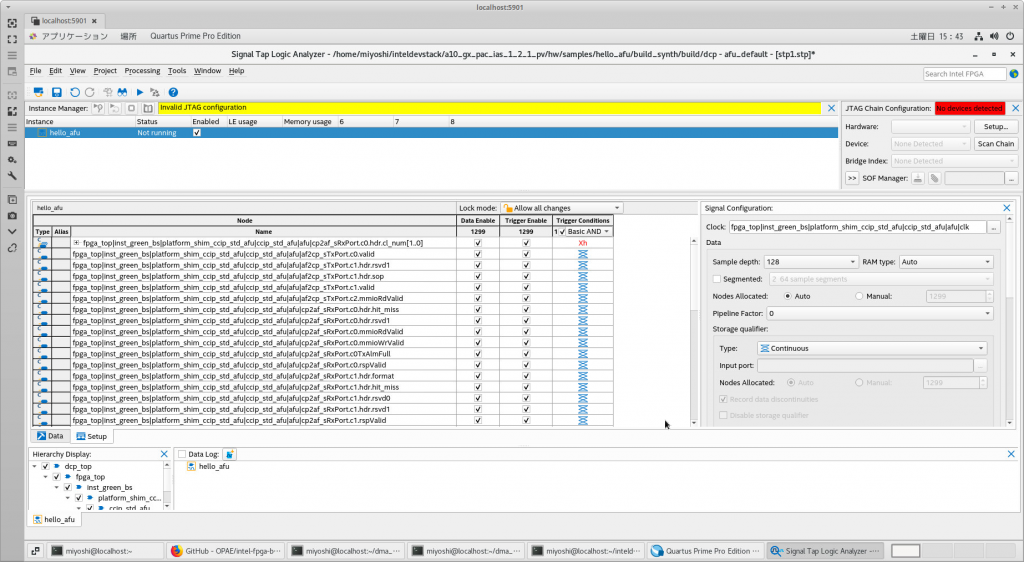

一通り設定が終わると、こんな感じになっているはずです。

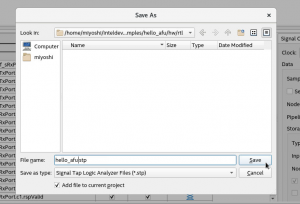

メニューのFile -> Save とたどるか、メニュー下のタブにあるフロッピーディスクのアイコンをクリックして保存します。ファイル名は、Signal Tapのインスタンス名に合わせて、hello_afu.stpとします。ファイルの保存先はビルドに利用した hello_afu/build_synth ディレクトリではなくてソースコードと同じ、hw/rtlの下にします。

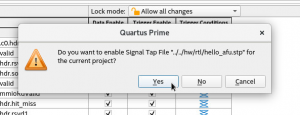

ファイルを保存した後、Signal Tap Logic Analyzerを閉じようとすると、デザインに組み込むか聞かれるダイアログが開くので、Yesをクリックします。

Signal Tap Logic Analyzerを閉じたら、Quartusも閉じます。

最後に、PACのビルドプロセスにstpファイルを組み込みます。具体的には、$OPAE_PLATFORM_ROOT/hw/samples/hello_afu/hw/rtl/filelist.txtの先頭に、以下の2行を追加します。

+define+INCLUDE_REMOTE_STP

hello_afu.stp追加したら、現在生成済のビルドセットの設定ファイルを上書きします。

$ rtl_src_config --qsf --rel build ../hw/rtl/filelist.txt > hw/afu.qsf上書きしたら、再度ビルドします。

$ ${OPAE_PLATFORM_ROOT}/bin/run.shビルドが終わったら、キーなしで利用できるように設定します。

$ PACSign PR -t UPDATE -H openssl_manager -i hello_afu.gbs -o hello_afu_unsigned.gbsデバッグする

まずは、FPGAをコンフィギュレーションします。

$ fpgaconf hello_afu_unsigned.gbs次にmmlinkを起動します。このプロセスを介して、プログラムはFPGAにアクセスします。

$ mmlink -P 3333 -B 0x18ここで、3333は mmlinkにアクセスするためのTCPのポート番号です。3333がデフォルトです。-B以降の0x18はFPGAが接続しているバスIDです。何を指定していいかわからない場合は、fpgainfo portを実行して、PCIeの s:b:d:f の b のb部分を見てみてください。ちなみに、うちの実行結果はこんな感じでした。

$ fpgainfo port

Board Management Controller, microcontroller FW version 26895

Last Power Down Cause: POK_CORE

Last Reset Cause: None

//****** PORT ******//

Object Id : 0xEC00000

PCIe s:b:d:f : 0000:18:00:0

Device Id : 0x09C4

Socket Id : 0x00

Ports Num : 01

Bitstream Id : 0x124000200000367

Bitstream Version : 1.2.4

Pr Interface Id : 38d782e3-b612-5343-b934-2433e348ac4c

Accelerator Id : 850adcc2-6ceb-4b22-9722-d43375b61c66

Boot Page : userさて、mmlinkを起動すると、次のような感じでプロセスが立ち上がって、接続待ちになります。

$ mmlink -P 3333 -B 0x18

------- Command line Input START ----

Bus : 24

Device : -1

Function : -1

Socket-id : -1

Port : 3333

IP address : 0.0.0.0

------- Command line Input END ----

PORT Resource found.

Remote STP : Assert Reset

Remote STP : De-Assert Reset

Read signature value 53797343 to hw

Read version value 1 to hw

Read write fifo capacity value 32 to hw

m_listen: 4

listening on ip: 0.0.0.0; port: 3333次は、mmlinkに対して接続するプログラムがsystem-consoleです。system-consoleを起動するためには、$OPAE_PLATFORM_ROOT/hw/remote_debug の下にある、mmlink_setup_profiled.tcl と remote_debug.sof が必要です。今回は、system-console を $OPAE_PLATFORM_ROOT/hw/samples/hello_afu/hw/rtl/ で利用することにして作業してみます。

$ cd $OPAE_PLATFORM_ROOT/hw/samples/hello_afu/hw/rtl/

$ cp $OPAE_PLATFORM_ROOT/hw/remote_debug/* .

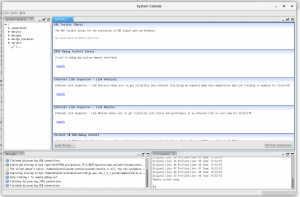

$ system-console --rc_script=mmlink_setup_profiled.tcl remote_debug.sof localhost 3333 &ここで、localhostはmmlinkが起動しているホスト、3333はmmlink起動時に指定したポート番号です。system-consoleが無事起動すると、次のようなウィンドウが表示されます。

右下のコンソール部分に、Remote system readyと表示されるはずです。

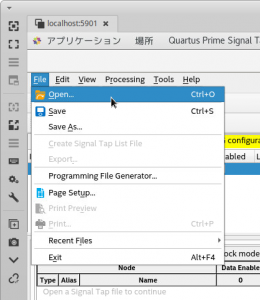

最後に、Signal Tap Logic Analyzerを起動します。手っ取り早くスタンドアロンで起動したいので、

$ quartus_stpwとターミナルで入力しましょう。

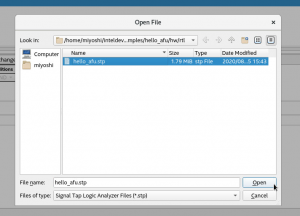

起動したら File->Open で作成した hello_afu.stp を開きます。

ファイルを開いたら、画面右側にある、JTAG Chain Configurationペインにある Hardware の右のセレクトボックスを開いて、System Console on… を選択します。これがsystem-console→mmlinkを経由してPACにアクセスする設定に相当します。

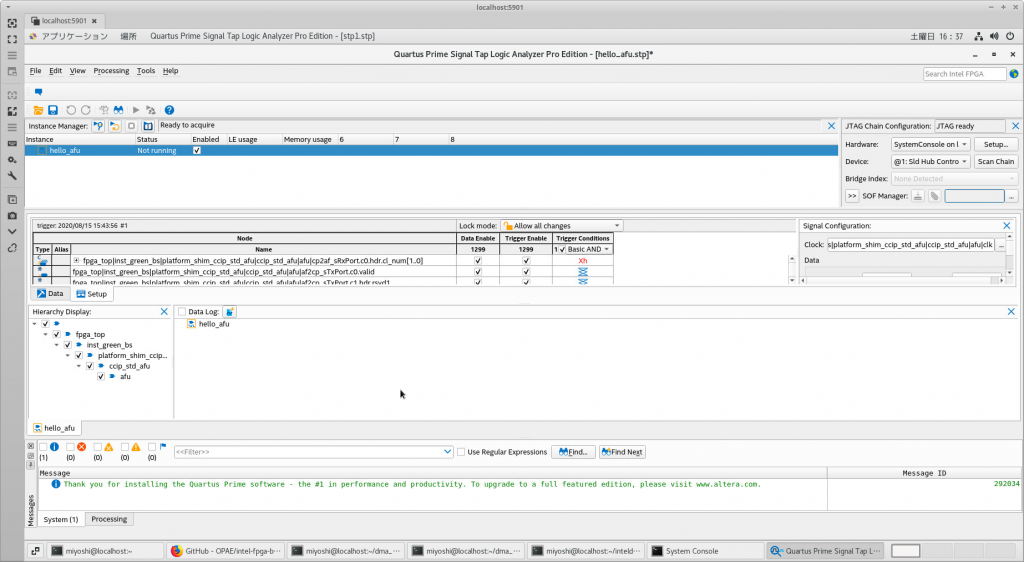

一通り設定が終わると、次のように、JTAG Chain Configurationの右側が JTAG readyになり、また、メニューの下にあるInstance Manager の右のテキストフィールドがReady to acquireになります。黄色や赤のままのフィールドがないことが正しく動作している証です。

これで、Signal Tapを利用するまでの準備はおしまいです。とりあえず、トリガをかけてみると信号を読み取ることができます。

プログラムと併用する

PACをデバッグする場合、多くはFPGA単体ではなくソフトウェアで操作したときの波形を確認したいはずです。hello_afuはじめ多くのサンプルはデフォルトのままではmmlinkが起動している状態でFPGAをオープンできません。mmlinkとFPGAを共有できるようにプログラムを変更する必要があります。

具体的な方法をhello_afuサンプルで確認します。まず、ソフトウェアをビルドして実行してみましょう。

$ cd $OPAE_PLATFORM_ROOT/hw/samples/hello_afu/sw

$ make

$ ./hello_afuすると、

Error opening AFC: resource busy

Test FAILED!といっておこられます。これは上述の通り、mmlinkがFPGAにアクセスしているから、です。これを回避するためには、hello_afu.c を修正します。 hello_afu.c を開いて、fpgaOpenを探し第三引数を 0 から FPGA_OPEN_SHARED に変更します。

/* Open AFC and map MMIO */

res = fpgaOpen(afc_token, &afc_handle, FPGA_OPEN_SHARED);

ON_ERR_GOTO(res, out_destroy_tok, "opening AFC");変更して再度ビルドして実行すると、

$ make

...

$ ./hello_afu

Running Test

AFU DFH REG = 1000010000000000

AFU ID LO = 9722d43375b61c66

AFU ID HI = 850adcc26ceb4b22

AFU NEXT = 00000000

AFU RESERVED = 00000000

Reading Scratch Register (Byte Offset=00000080) = 00000000

MMIO Write to Scratch Register (Byte Offset=00000080) = 123456789abcdef

Reading Scratch Register (Byte Offset=00000080) = 123456789abcdef

Setting Scratch Register (Byte Offset=00000080) = 00000000

Reading Scratch Register (Byte Offset=00000080) = 00000000

Done Running Testと、正しく実行することができます。

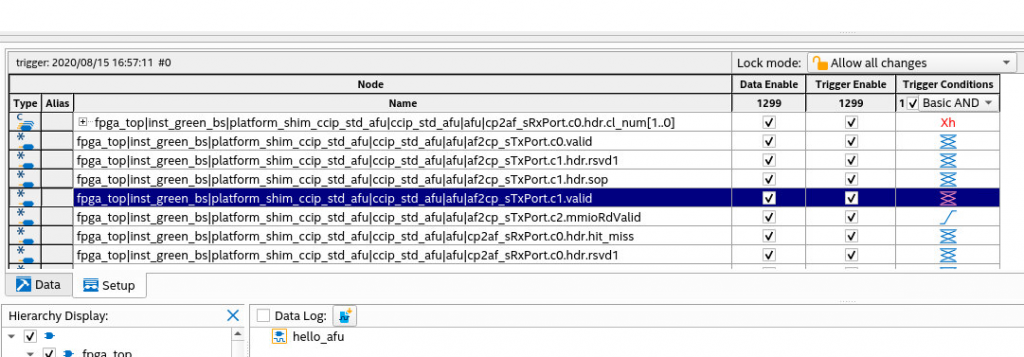

たとえば、次のように af2cp_sTxPort.c2.mmioRdValid の立ち上がりでトリガをかけた状態でプログラムを実行してみます。

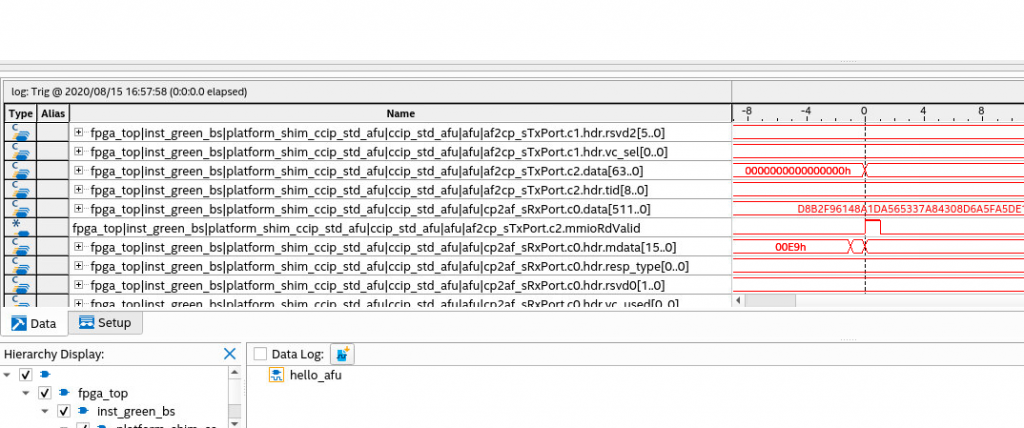

すると、プログラムによってレジスタアクセスが発生し、afuからデータが転送されるタイミングの波形を確認することができました。

ピンバック: Intel PAC向けに既存のstpファイルを埋め込む | わさらぼ