Design Solution Forumにて”オープンソース高位合成処理系 Synthesijer”とういタイトルで発表させていただきました.

内容は,Synthesijerを使った開発のイメージと,どういうつもりでSynthesijerを開発しているか,というものを盛り込んだものになっています.

発表資料は,http://www.dsforum.jp/materials/ からダウンロードできるようです.

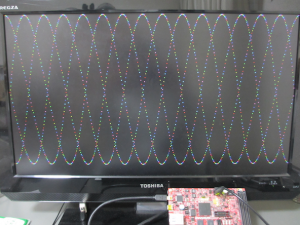

例題としては,東京エレクトロンデバイスのZynq評価ボードを使った画像表示回路として,位相の違うsinカーブを描く回路(Javaコード)を紹介してみました.関連リソースは少し整理をして10月末までには公開したいと計画中です.