GitHubで公開されてているKria-PYNQのbaseをビルドしてみる.ライセンスは https://github.com/Xilinx/Kria-PYNQ/blob/main/LICENSE によるとBSD 3-Clause License なので,オリジナル作るときはこれをベースにすすめればよさそう.というわけでビルドして生成されたVivadoプロジェクトなどを眺めてみました,という話.

手順は,kv260/base/README.md 通り,make 一発.

$ git clone https://github.com/Xilinx/Kria-PYNQ.git

$ cd Kria-PYNQ

$ git checkout v3.0

$ git submodule update --init --recursive

$ source /tools/Xilinx/Vitis/2020.2/settings64.sh

$ kv260/base

$ makeVivado/Vitis HLSの日付のバグを踏むので https://support.xilinx.com/s/article/76960 をちゃんと当てとかないとダメ.また,2020.2.2のアップデートをインストールしとくのとKV260のボードファイルを用意しておく必要があるのは注意.ボードファイルは,https://github.com/Xilinx/XilinxBoardStore/tree/2020.2.2/boards/Xilinx/kv260 を たとえば, /tools/Xilinx/Vivado/2020.2/data/boards/board_files にコピーしとく.

ビルドがおわると,PYNQでPLをオーバーレイするのに必要な

- base.bit

- base.hwh

- base.dtbo

が生成される.

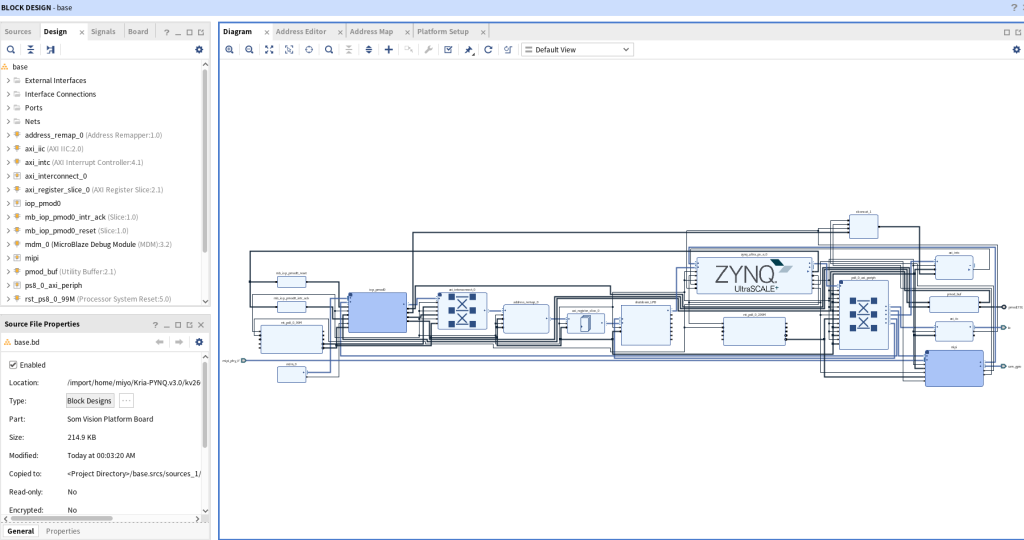

base/base.xpr を開いてブロックデザインをみてみると↓のような感じ.ロゴが入っているのがZYNQ UltraSCALE+.左側の濃いブロックがiop_pmod0でPMODにつながっていて,

右側の濃いブロックはmipi.

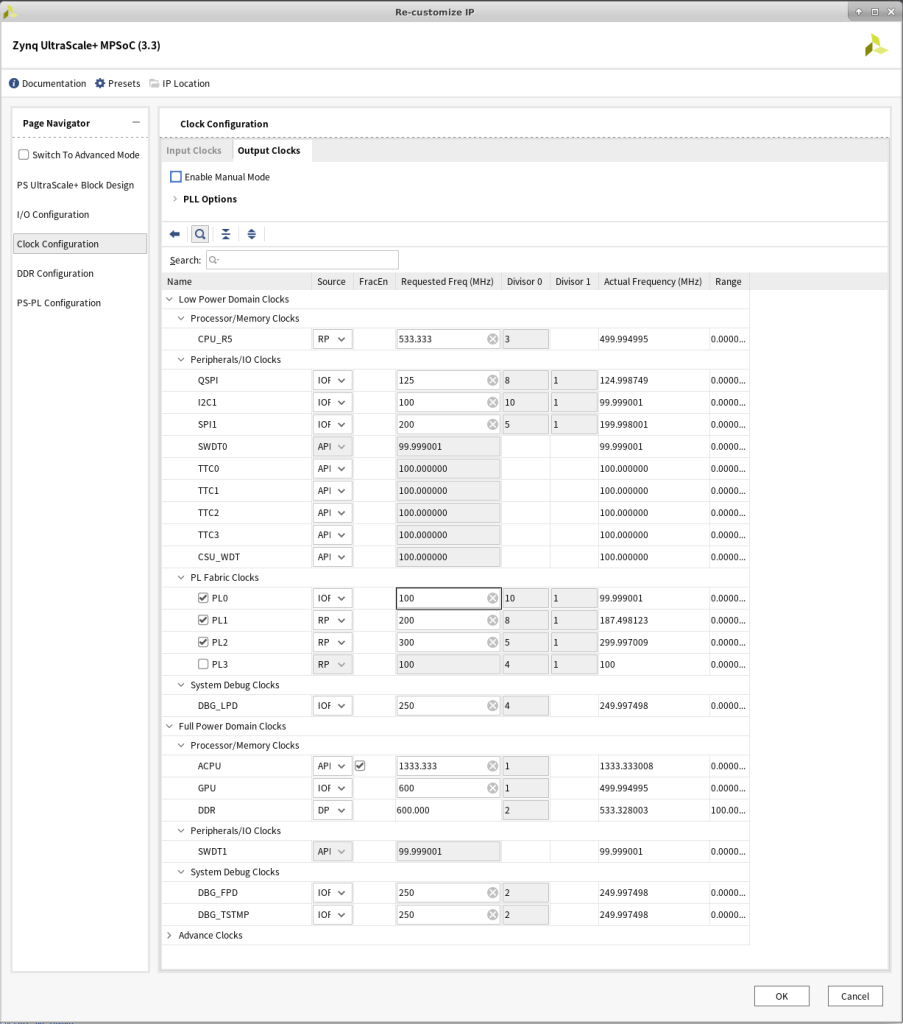

Zynq ULTRASCALE+のクロックの設定はこんな感じ

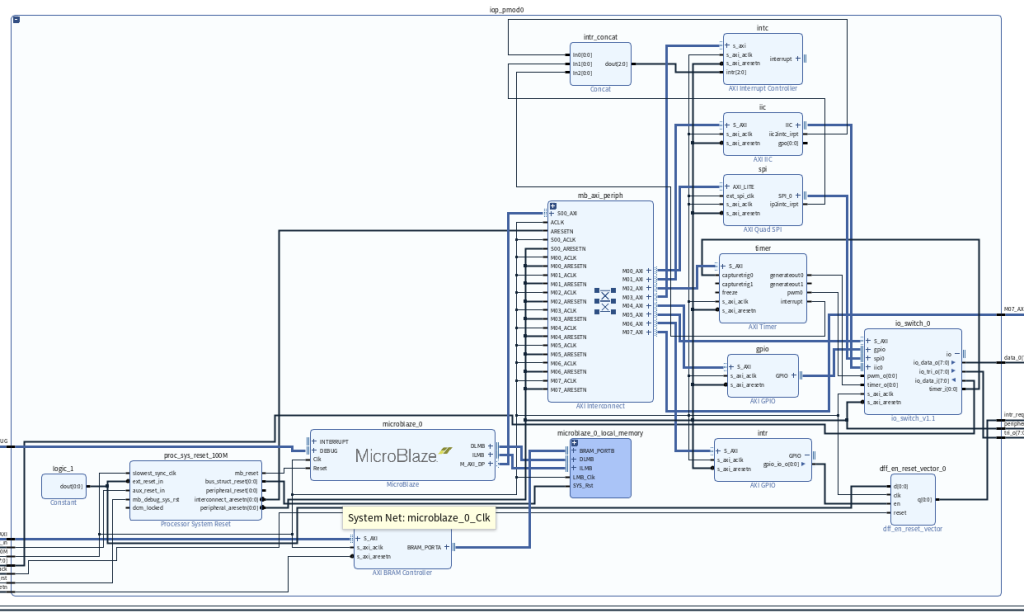

iop_pmod0の中身はこんな感じ.中にMicroBlazeがいる.

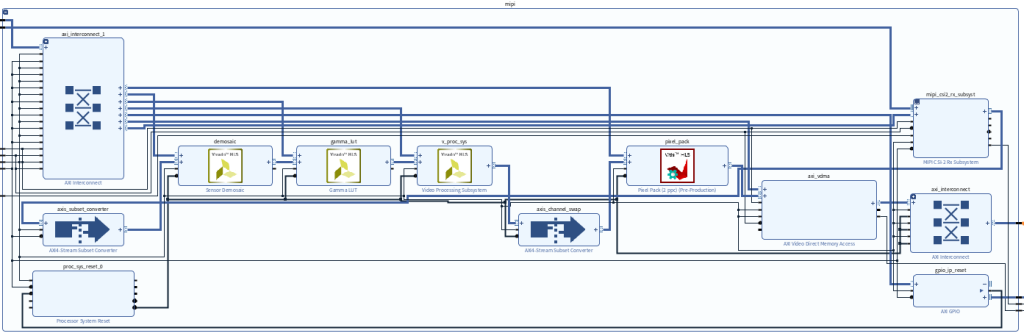

mipiの中身はこんな感じ.Vitis HLSで作ったモジュール達が入っている.入力はmipi_phy_ifで外部から入っていて,計算した結果はAXI Video Direct Memory Accessを介してZynq UltraSCALE+のS_AXI_HPI_FPDに入力されている.