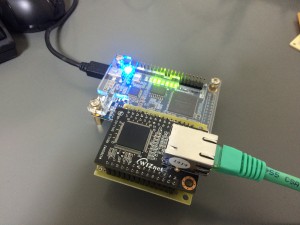

とある親切な方に,WIZ830MJをわけていただいたので,DE0-nanoに接続してみました.

WIZ830MJに載っているW5300は,制御/ステータスレジスタやパケット格納メモリがメモリアドレス空間にマッピングされた,プロセッサとの親和性が高いインターフェースを持っています.

正当なAlteraユーザであれば,おそらくNios IIにぶらさげるところなのでしょうが,まずは,(私にとって)てっとり早くSynthesijerで制御回路を書いてみました.

制御コードは↓.

https://github.com/miyo/de0nano/blob/master/wiz830mj/WIZ830MJ_Test.java

W5300のI/FはSRAM相当なのでJavaの配列にマッピングすることもできますが,CS,WR,RDの遅延を適当にエミュレーションできるように,read/writeのメソッドを定義しています.ちなみに,read/writeのデータがbyteなのは,16bitバスを全部半田づけするのが面倒で8bit接続しているからです.

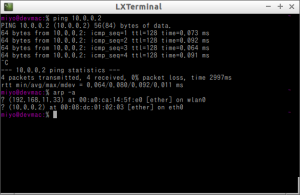

実際にW5300を制御(初期化)しているのは,testメソッド.ここでは,ping通ることが確認できるように,ネットワークの設定だけしています.

QuartusIIで合成する場合には,SynthesijerでHDLに変換したコード,Javaコード中でインスタンシエーションしているWIZ830MJ_Iface(WIZ830MJ_Iface.java)に相当するwiz830mj_iface.vhd,トップモジュールであるtop.vhdを使います.

また,ピン制約がwiz830mj_test.qsf,クロック制約がwiz830mj_test.sdcです.

合成してsofを書き込むと,無事pingが帰ってきました.arpでMACアドレスが取得できていることも分かります.

さて,次は,TCPやUDPで遊んでみましょう.